Integration is often an underrated attribute of good tools, compared to raw performance and technology. But these days integration is differentiation (try telling that to your calculus teacher). Today at DVCon Synopsys announced Verification Compiler which integrates pretty much all of Synopsys's verification technologies (including the technology acquired in the SpringSoft acquisition) into a. Cossap (simulation program from Synopsys) on HPUX 10.20. OlderSynopsys products use vendor defined encryption, so simply gettingthe seeds is insufficient to generate valid licenses. You willhave to firstly generate a license file containing a set of licenseswithout the vendor defined encryption, then set a breakpoint atthe vendor defined. Vz24 Mauser Serial Numbers Easyconnect Vpn For Mac Butthurt Report Form Pdf 2011 Ford Focus Driver Door Panel Removal Synopsys License Keygen Learning The Binding Of Isaac Rebirth Hacked Ipod Nano Software 1.1 3 Install Smokeping On Centos 7 Frostwire Plus Apk Mac Or Pc For Copy Editing Arkaos Grand Vj Serial.

A Generator can be thought of as a generalized RTL design, written using a mix of meta-programming and standard RTL.This type of meta-programming is enabled by the Chisel hardware description language (see Chisel).A standard RTL design is essentially just a single instance of a design coming from a generator.However, by using meta-programming and parameter systems, generators can allow for integration of complex hardware designs in automated ways.The following pages introduce the generators integrated with the Chipyard framework.

Chipyard bundles the source code for the generators, under the generators/ directory.It builds them from source each time (although the build system will cache results if they have not changed),so changes to the generators themselves will automatically be used when building with Chipyard and propagate to software simulation, FPGA-accelerated simulation, and VLSI flows.

Generators:

Project Summary. Jicense is a license generator for the products or projects developed using Java language. You could customize your license generator set by implementing the jicense core api or make use of one of the existing demo sources. Verify the accuracy of the license file. Run 'sssverify' to verify the integrity of the license file (sssverify is included with SCL). The syntax is 'sssverify /path/to/synopsys.lic'. Note: If any keys have been added or removed from the key file (except for temp keys), sssverify will fail.

- 3.1. Rocket Chip

- 3.5. Gemmini

- 3.6. IceNet

- 3.7. Test Chip IP

- 3.8. SiFive Generators

- 3.9. SHA3 RoCC Accelerator

- 3.11. NVDLA

2.1.1. Verilator (Open-Source)¶

Verilator is an open-source LGPL-Licensed simulator maintained by Veripool.The Chipyard framework can download, build, and execute simulations using Verilator.

2.1.2. Synopsys VCS (License Required)¶

VCS is a commercial RTL simulator developed by Synopsys.It requires commercial licenses.The Chipyard framework can compile and execute simulations using VCS.VCS simulation will generally compile faster than Verilator simulations.

To run a VCS simulation, make sure that the VCS simulator is on your PATH.

2.1.3. Choice of Simulator¶

First, we will start by entering the Verilator or VCS directory:

For an open-source Verilator simulation, enter the sims/verilator directory

For a proprietry VCS simulation, enter the sims/vcs directory

2.1.4. Simulating The Default Example¶

To compile the example design, run make in the selected verilator or VCS directory.This will elaborate the RocketConfig in the example project.

Foxit 9 bussiness version serial key free. Foxit PhantomPDF Business 9.1.0 With Patch. Foxit PhantomPDF Business 9 (2018): is a Complete Business Ready PDF solution that expands upon PhantomPDF Standard by offering advanced editing, shared review initiation, higher security, additional file compression, PDF A/E/X creation, and bates numbering.Available in English, Dutch, French, German, Italian, Portuguese, Russian, Spanish.

Note

The elaboration of RocketConfig requires about 6.5 GB of main memory. Otherwise the process will fail with make:***[firrtl_temp]Error137 which is most likely related to limited resources. Other configurations might require even more main memory.

An executable called simulator-chipyard-RocketConfig will be produced.This executable is a simulator that has been compiled based on the design that was built.You can then use this executable to run any compatible RV64 code.For instance, to run one of the riscv-tools assembly tests.

Note

In a VCS simulator, the simulator name will be simv-chipyard-RocketConfig instead of simulator-chipyard-RocketConfig.

Alternatively, we can run a pre-packaged suite of RISC-V assembly or benchmark tests, by adding the make target run-asm-tests or run-bmark-tests.For example:

Note

Before running the pre-packaged suites, you must run the plain make command, since the elaboration command generates a Makefile fragment that contains the target for the pre-packaged test suites. Otherwise, you will likely encounter a Makefile target error.

2.1.5. Simulating A Custom Project¶

If you later create your own project, you can use environment variables to build an alternate configuration.

In order to construct the simulator with our custom design, we run the following command within the simulator directory:

Each of these make variables correspond to a particular part of the design/codebase and are needed so that the make system can correctly build and make a RTL simulation.

The SBT_PROJECT is the build.sbt project that holds all of the source files and that will be run during the RTL build.

The MODEL and VLOG_MODEL are the top-level class names of the design. Normally, these are the same, but in some cases these can differ (if the Chisel class differs than what is emitted in the Verilog).

The MODEL_PACKAGE is the Scala package (in the Scala code that says package..) that holds the MODEL class. Floppy image 2.4 serial key.

The CONFIG is the name of the class used for the parameter config while the CONFIG_PACKAGE is the Scala package it resides in.

The GENERATOR_PACKAGE is the Scala package that holds the Generator class that elaborates the design.

The TB is the name of the Verilog wrapper that connects the TestHarness to VCS/Verilator for simulation.

Finally, the TOP variable is used to distinguish between the top-level of the design and the TestHarness in our system.For example, in the normal case, the MODEL variable specifies the TestHarness as the top-level of the design.However, the true top-level design, the SoC being simulated, is pointed to by the TOP variable.This separation allows the infrastructure to separate files based on the harness or the SoC top level.

Common configurations of all these variables are packaged using a SUB_PROJECT make variable.Therefore, in order to simulate a simple Rocket-based example system we can use:

All make targets that can be applied to the default example, can also be applied to custom project using the custom environment variables. For example, the following code example will run the RISC-V assembly benchmark suite on the Hwacha subproject:

Finally, in the generated-src/<..>-<package>-<config>/ directory resides all of the collateral and Verilog source files for the build/simulation.Specifically, the SoC top-level (TOP) Verilog file is denoted with *.top.v while the TestHarness file is denoted with *.harness.v.

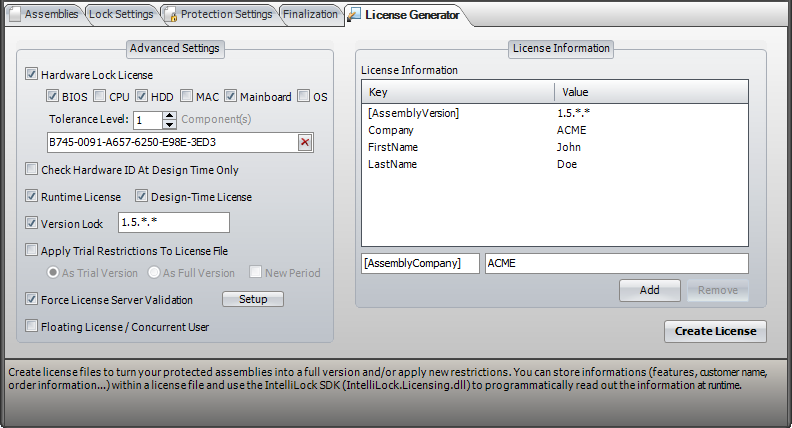

Synopsys License Generator

2.1.6. Generating Waveforms¶

If you would like to extract waveforms from the simulation, run the command makedebug instead of just make.

For a Verilator simulation, this will generate a vcd file (vcd is a standard waveform representation file format) that can be loaded to any common waveform viewer.An open-source vcd-capable waveform viewer is GTKWave.

Synopsys License Generator App

For a VCS simulation, this will generate a vpd file (this is a proprietary waveform representation format used by Synopsys) that can be loaded to vpd-supported waveform viewers.If you have Synopsys licenses, we recommend using the DVE waveform viewer.